當前位置: 首頁 > 工業電子產品 > 其他電子產品 > 開發板,套件,編程器 > 開發板

發布日期:2022-10-14 點擊率:371

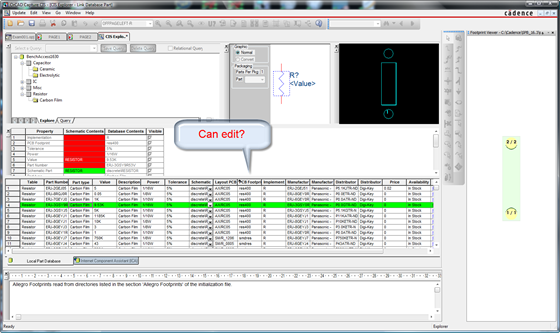

OrCAD Capture CIS是Cadence公司的一款原理圖設計軟件,其便捷性,專業性贏得了廣大工程師的喜愛。對于剛剛參加工作的讀者來說,可能一開始很不適應OrCAD Capture CIS,因為這款軟件與之前在學校學習的Protel很不像。在此,我奉上這篇初學者快速上手指導教程,希望能對剛剛學習OrCAD Capture CIS的讀者有幫助。根據我自己的經驗,對新的軟件我一般會采用兩步曲:第一步是快速上手,第二步是學習一些常用的功能,所以我就按這個順序來介紹Capture CIS軟件的使用吧.

OrCAD Capture CIS快速上手

安裝好軟件后,安裝點擊如下圖所示的Design Entry CIS。

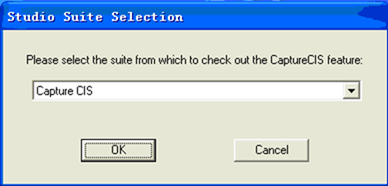

會彈出如下圖所示的對話框,選擇Capture CIS,點擊OK。

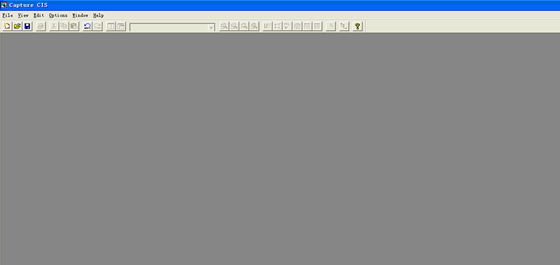

系統會彈出下圖所示的界面。

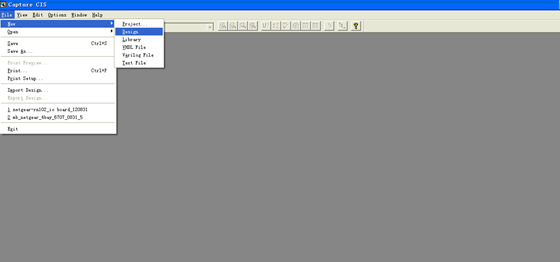

在彈出的界面中點擊File->New->Design

注意:Project和Design的區別是一個Project可以包含很多的Design, 我們在使用中一般選擇Design。

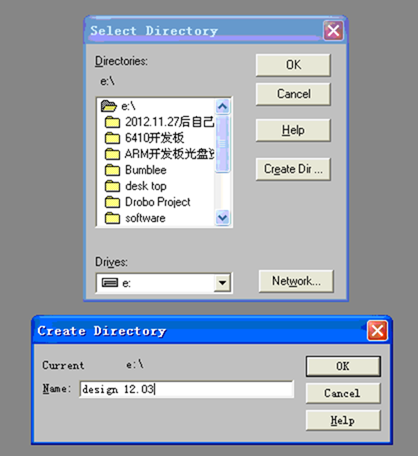

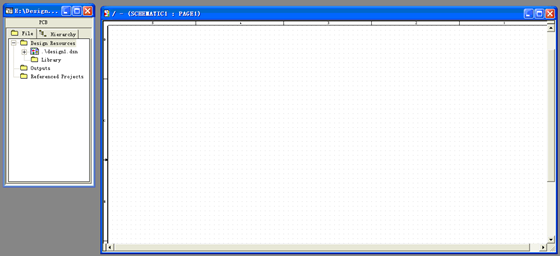

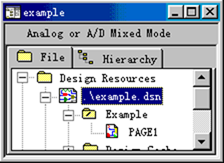

在彈出的對話框中選擇你保存你的設計,然后點擊OK, 就會彈出如下圖所示的設計界面。

對一個新的設計,首先應該是選擇設計的圖紙的大小,在無線時代,都用B號圖紙。

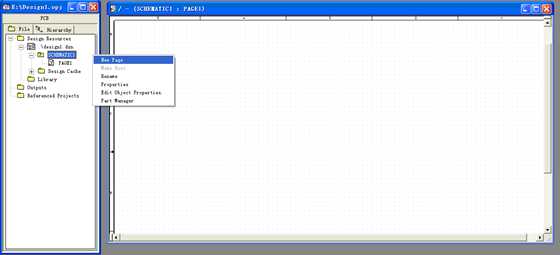

好了,在新彈出的對話框中,你可以右鍵圖中的SCHEMATIC1, 在彈出的下拉單中選擇New Page, 然后重命名,你可以根據設計的需要設計Page 的數量。

OrCAD Capture CIS常用功能介紹

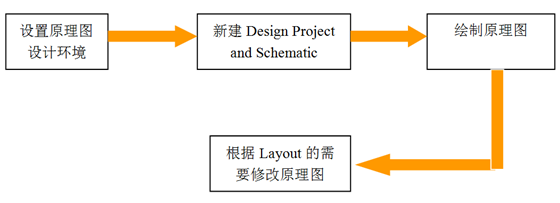

1. Capture CIS設計過程

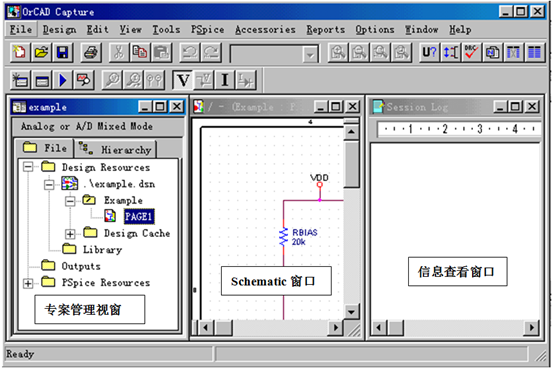

2. Capture CIS操作環境

Capture CIS有三個主要工作窗口:

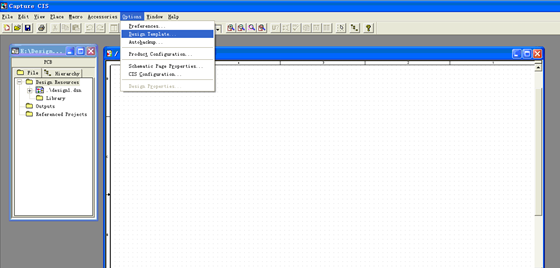

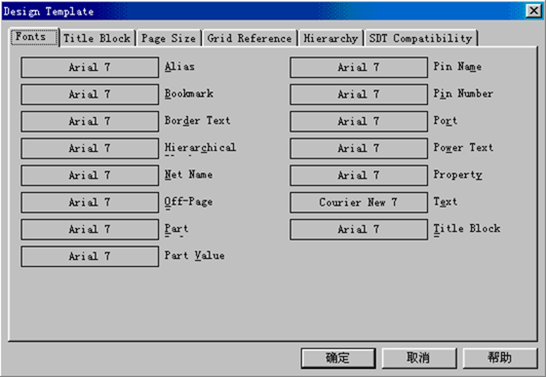

3. Capture設計參數設置

Capture的環境參數包括:系統屬性及設計模板兩大類。

系統屬性包括(Options->Preferences):

系統設計模板參數包括(Options->Design Template):

我們都是用B號圖紙,所以這個基本不會重新設置。

4. 開始繪制電路圖

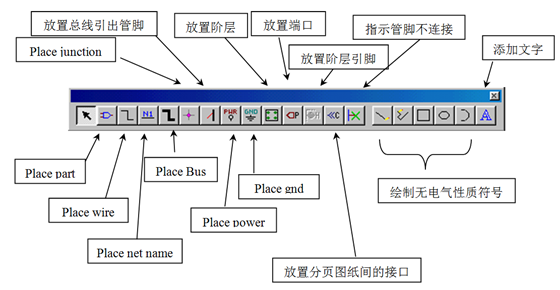

新建Design后,進入Schematic窗口,則在窗口右邊會出現下圖的工具欄:

4.1 Place part(放置器件)

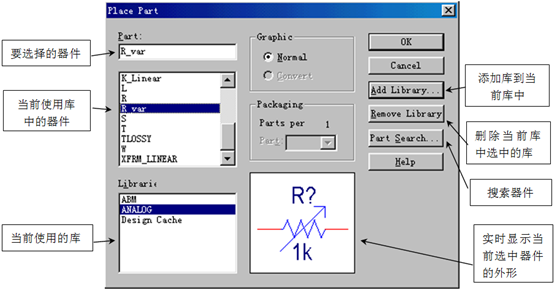

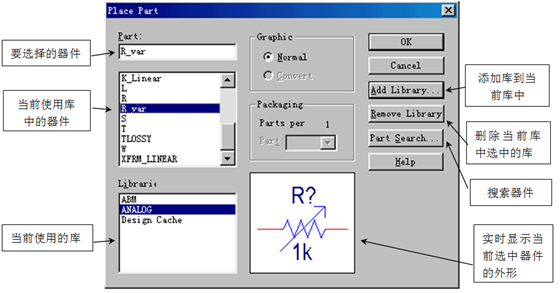

在Capture CIS中,找元器件非常的方便,可以很容易查找并調出使用。點擊Place part快捷按鈕或點擊Place->Part將調出如下對話框:

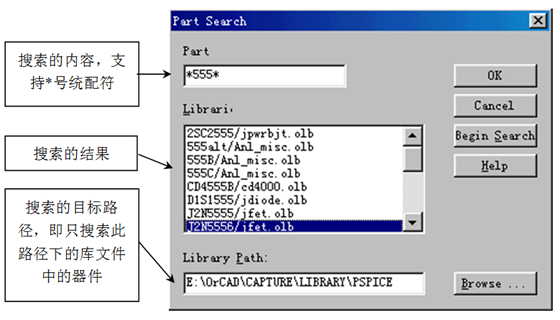

點擊Part Search…按鈕,調出下面的器件搜索對話框:

4.2 連線及放置數據總線(Place wire or bus)

4.2 連線及放置數據總線(Place wire or bus)

點擊Place wire(或place bus)按鈕進入連線(或放置數據總線)狀態,此時鼠標變成十字形,移動鼠標,點擊左鍵即可開始連線(或放置數據總線)。連線時,在交叉而且連接的地方會有一個紅點提示,如果你需要在交叉的地方添加連接關系,點擊place junction,把鼠標移動到交叉點并點擊左鍵即可。放置數據總線后,點擊place bus entry按鈕放置數據總線引出管腳,管腳的一端要放在數據總線上。

4.3 放置網絡名稱(place net name)

點擊place net alias按鈕,調出place net alias對話框,在alias對話框中輸入要定義的名稱,然后點擊OK退出對話框,把鼠標移動到你要命名的連線上,點擊鼠標左鍵即可。

注意:數據總線與數據總線的引出線一定要定義網絡名稱。

4.4 放置電源和地(place power or GND)

點擊Place Power(或Place GND),調出如下對話框:

4.5 放置端口與分頁圖紙間的接口

點擊Place Hierarchical Port(或place Off-page connector)放置端口(或分頁圖紙間的接口),調出如下對話框:

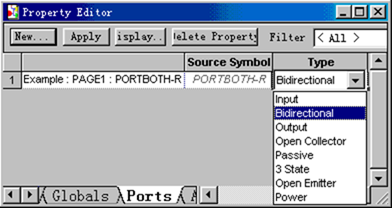

對于端口,不同端口之間的區別在于其類型的不同,它的類型可以從它的TYPE屬性中得知,雙擊端口或選中端口并點擊右鍵在彈出菜單中選擇Edit Properties,調出如下窗口:

對于端口,不同端口之間的區別在于其類型的不同,它的類型可以從它的TYPE屬性中得知,雙擊端口或選中端口并點擊右鍵在彈出菜單中選擇Edit Properties,調出如下窗口:

4.6 添加文字(Place Text)

4.6 添加文字(Place Text)

點擊Place Text…按鈕,系統彈出如下對話框:

5. 原理圖繪制后續處理

5. 原理圖繪制后續處理

原理圖繪制好之后,接下來就是對電路圖進行DRC檢測,生成網表及材料清單。

注意:對原理圖進行后續處理,在Capture中必須切換到專案管理窗口下,并且選中*.DSN文件。

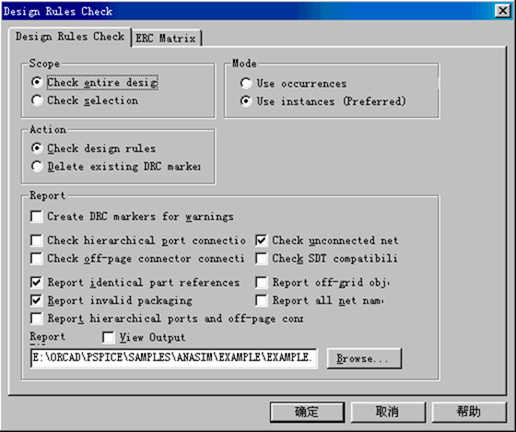

5.1 DRC檢測(Design Rules Check)

點擊DRC檢測按鈕或(Tools->Design Rules Check),調出如下設置對話框:

Scope:

Mode:

Action:

Report:DRC檢測的內容

5.2 與DRC檢測相對應的自動排序功能

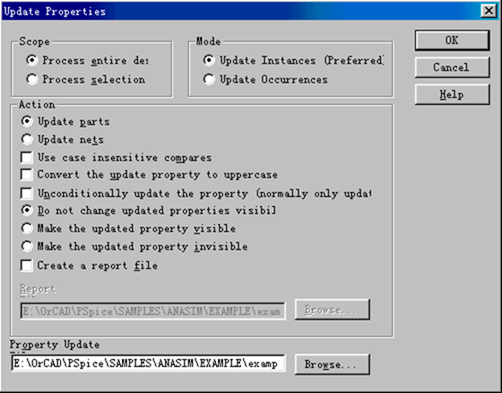

通常,我們需要對自己設計的原理圖中的器件編號進行從新排序。Capture CIS提供自動排序功能,允許你對原理圖重新排序。

點擊Tools->Annotate,調出如下對話框:

Scope:

Action:

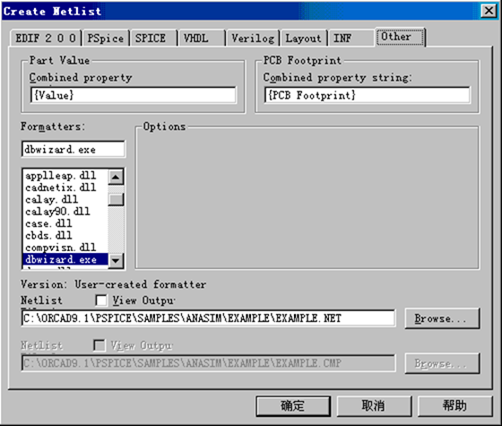

5.3 生成網絡表

對于Capture CIS來說,生成Netlist也是非常方便的,Netlist的作用是幫助layout工程師生成PCB文件。

點擊Tools>Create Netlist…,調出如下對話框

在對話框中選擇您需要的EDA軟件格式,我們都選Allegro, 點擊確定即可生成相應的網絡表。網絡表是提供給Layout工程師的,他們在Allegro中導入Netlist就能生成待布線的PCB文件。

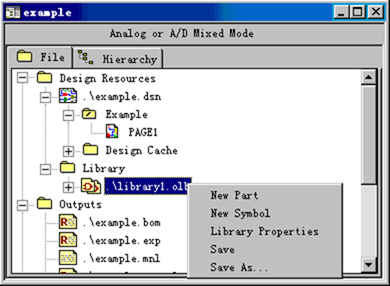

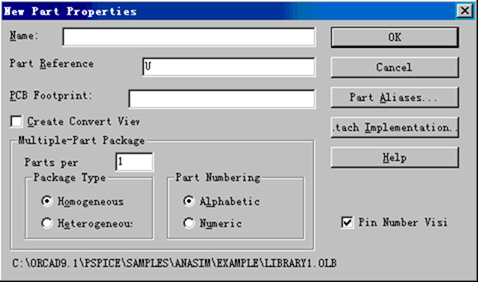

5.4 建立器件圖形符號庫

本文來自合作伙伴投稿,作者Robin, Jiang,郵箱804037583@qq.com。

下一篇: PLC、DCS、FCS三大控

上一篇: Ralink RT3052 WLAN S