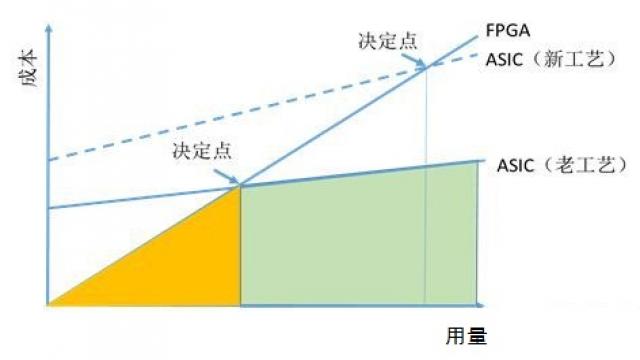

作為一個系統(tǒng)設(shè)計工程師,經(jīng)常會遇到這個問題:是選用ASIC還是FPGA?讓我們來看一看這兩者有什么不同。