發布日期:2022-10-09 點擊率:66

引言

傳統的邏輯分析儀體積龐大、價格昂貴、通道數目有限,并且在數據采集、傳輸、存儲、顯示等方面存在諸多限制,在很大程度上影響了其在實際中的應用。選用高性能的FPGA芯片進行數據處理,充分利用PC的強大處理功能,配合LabView圖形化語言開發的虛擬邏輯分析儀,其數據處理和傳輸速率大大提高,適用性極大增強,其顯示、操作界面和低廉的成本較之傳統的邏輯分析儀具有極大的優勢和發展前景。

工作原理

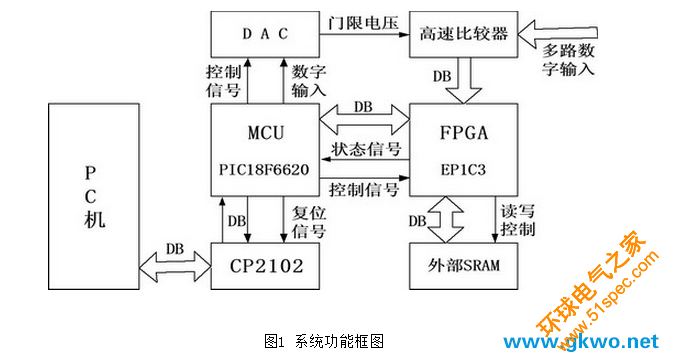

本設計選用Altera公司的Cyclone系列FPGA器件EP1C3進行數據采集和處理,外接SRAM,用于數據的存儲。系統通過高性能的PIC單片機PIC18F6620完成與PC的通信,接收PC發出的觸發、配置信息并控制系統將采集處理后的數據上傳至PC顯示。單片機與PC的接口利用符合USB2.0規范的接口芯片CP2102實現。

首先,PC向FPGA發送觸發字信息、數據采集控制信息和開啟數據采集信號;單片機發送數據至外接DAC產生門限電壓;采集到的輸入信號通過高速比較器與此門限電壓進行比較,以確定其值為0或1。接收到PC發出的開啟數據采集信號后,FPGA按設定的工作方

式采集數據,各通道數據移位輸入FPGA內部緩存并存入外部SRAM。FPGA將緩存中存儲的采集數據與設定的觸發字、觸發方式和屏蔽位進行比較。一旦符合觸發條件,則設置觸發標志,記錄觸發位置。當數據采集至設定的點數后,FPGA向PC發送采集完成信號。上位機接收到此信號后,發送讀取數據命令,系統讀回采集數據并在PC屏上顯示。系統功能框圖如圖1所示。

系統觸發模塊設計

觸發模塊是整個系統的核心部分,主要包括采樣時鐘選擇模塊、觸發電平設置和觸發電路三個部分。

采樣時鐘選擇模塊

時鐘選擇模塊用于選擇采樣頻率。可供選擇的時鐘源包括:外部時鐘(由有源晶振提供)、單片機PWM模塊產生的PWM時鐘、外部時鐘輸入(由額外的設備提供)、以第N路數字信號輸入作為采樣時鐘。

觸發電平設置

觸發電平用來確定系統正確識別采樣信號的高低電平。該模塊由串行數模轉換器TLC5615和高速比較器LT1721構成。采樣開始前,單片機向DAC發送觸發電平數據,轉換后的電平信號(范圍從0~+5V)送入高速比較器。

觸發電路

觸發電路的作用是判斷采樣信號是否滿足觸發條件,并分別產生觸發動作。當采集的信號滿足用戶設置的觸發條件時,系統記錄觸發位置并產生觸發信號通知上位機讀取、顯示采樣數據。本次設計的觸發電路具有三種可選的觸發模式:立即觸發、順序觸發和并行觸發。

立即觸發

當上位機向FPGA發出立即觸發觸發字和開始采樣指令后,FPGA開始采樣并立即產生觸發信號。采樣電路將采集到的信號存入外部的SRAM中,直至采集到規定的點數后停止采樣,向上位機發出采樣結束信號,通知其讀取采樣數據。此方式下讀回的觸發點位置為0。

順序觸發

該方式設置了一個8位的序列觸發,只有當被測通道的信號按依次滿足觸發字所設定的8位序列時,才產生觸發信號。同時,為了操作的靈活性,還加入了屏蔽位。若對某一位的數據不敏感,可以將其對應的屏蔽位設置為0,在判斷觸發條件時不對該位進行檢測。

使用順序觸發方式,可以對任意一個通道選擇最多8位長度的序列進行觸發。在進行觸發設置時,除設置觸發方式(選擇順序觸發)和進行采樣頻率選擇以外,還需要進行通道選擇、觸發字和屏蔽位設置。其VerilogHDL算法源程序如下:

if(((dbuf^{TrigWord[1],TrigWord[0]})&{enbit[1],enbit[0]})==8'h00)

begin

TrigFlag=2'b01;Trigpoint[6:0]<=MemABus_Wr[6:0];

end

其中:dbuf為所測采樣通道的數據緩存;TrigWord[0]、TrigWord[1]為觸發字;enbit[0]、enbit[1]為屏蔽字;Trigpoint為觸發位置寄存器。

并行觸發

該方式設置了一個八級深度的并行觸發,將每次采樣得到的4個通道的數據組合為一個十六進制數,對應于一個4位的觸發字,當4個通道的數據在時間上依次滿足8個4位的觸發字時(并非要求連續),產生觸發信號。同樣,可以使用屏蔽位對某一通道的數據進行屏蔽,即在進行并行觸發檢測時,不對該路通道進行檢測。

使用并行觸發方式,可以選擇最多八級的并行觸發。在進行觸發設置時,除設置觸發方式(選擇并行觸發)和進行頻率選擇以外,還需要進行觸發字、屏蔽位和并行深度的設置。其VerilogHDL算法源程序如下:

if((({dbuf4[0],dbuf3[0],dbuf2[0],dbuf1[0]}^TrigWord[dcount])&enbit[0])==4'h0)

begin

if(dcount[2:0]==control[4:2])

begin

TrigFlag=2'b01;Trigpoint[6:0]<=MemABus_Wr[6:0];

dcount="3"'b000;end

dcount=dcount+3'b001;

end

其中,dbuf4、dbuf3、dbuf2、dbuf1分別為采樣通道4、3、2、1的數據緩存;TrigWord[dcount]為觸發字;dcount為觸發深度計數器;control[4:2]為設定的觸發

深度;enbit[0]為屏敝字;Trigpoint為觸發位置寄存器。

USB2.0接口設計

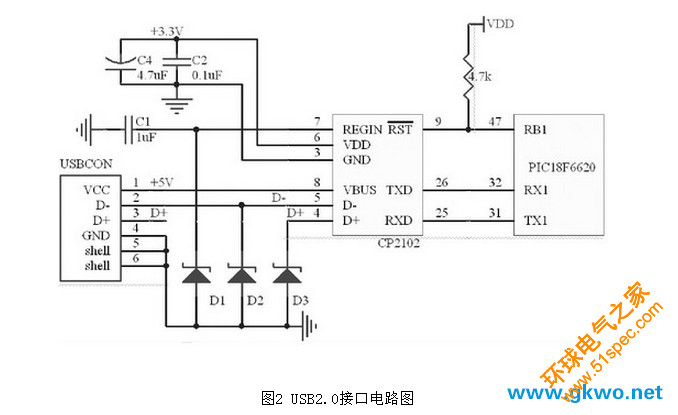

本設計選用符合USB2.0規范的CP2102芯片構建系統與PC的通信接口。

CP2102是USB-UART橋接芯片。該電路內置USB2.0全速功能控制器、USB收發器、晶體振蕩器、EEPROM及異步串行數據總線,支持調制解調器全功能信號,無需任何外部的USB器件。其功能強大,采用MLP-28封裝,尺寸僅為5mm×5mm,占用空間非常小,非常適合大數據量處理與傳輸電路系統的設計與應用。

實際應用中,系統只需使用CP2102基本的輸入/輸出數據線與復位信號線。其接口原理如圖2所示。

系統啟動時,單片機RB1端口發送一低電平至CP2102復位端,芯片復位,然后保持復位端高電平,CP2102正常工作。

由于CP2102內部的透明設計,數據通信時,可以不必構建CP2102與單片機的握手信號;CP2102數據線直接與單片機1#USART模塊的接收移位寄存器(RSR)和發送移位寄存器(TSR)相連。CP2102數據線上一旦出現待發送的數據,該數據會自動移入單片機接收移位寄存器;同樣,單片機發送數據時,發送移位寄存器中的數據直接移至CP2102的數據線(即USB接口數據線)上。

程序設計中,系統不斷檢測單片機接收中斷標志位RCIF1,一旦USART異步接收器的移位寄存器RSR接收到CP2102數據線上發送的停止位,RSR寄存器就將已接收的8位數據裝載到接收寄存器(RCREG1)中。系統發送數據時,前次裝入發送緩沖器(TXREG1)的數據的停止位P發送出去后,TXREG1緩沖器中的數據(軟件裝入)就被載入TSR寄存器中,TXREG1緩沖器就為空狀態,同時發送中斷標志位TXIF被置1。TSR將待發送數據逐位移至CP2102數據線,完成系統與CP2102USB模塊的數據傳輸。

軟件設計

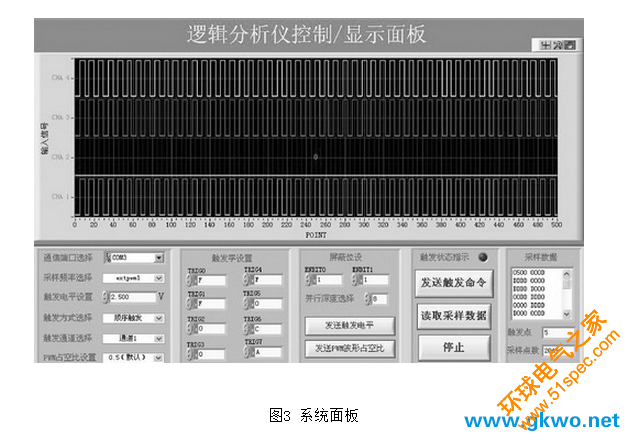

FPGA功能實現程序運用硬件描述語言VerilogHDL編寫;PIC單片機程序用C語言編寫,并采用第三方C語言工具HITECH公司PICC—18編譯器編譯實現。PC顯示和操作部分運用圖形化語言LabView7.1編寫,其前面板如圖3所示。

實驗操作

采用LabView7.1開發的虛擬操作平臺,可以方便實現儀器的操作控制。實驗開始前,首先選擇通信端口,建立PC與本系統的通信;設置觸發電平,設置采樣頻率(外部、內部或其他)、觸發方式、觸發字、屏蔽字并點擊“發送觸發命令”按鈕,完成相關設置,開啟數據采集和觸發進程。點擊“讀取采樣數據”可讀出采集到的數據,并在PC上顯示。

結語

在綜合考慮應用需要和成本的前提下,本設計采用4個高速采樣通道,最高可達75MHz采樣率,存儲深度達512KB,最多可采集220個測試點。觸發電平由10位串行數模轉換器TLC5615產生,電平誤差小于5mV。高速USB2.0通信接口配合LabView7.1開發的虛擬操作平臺,可實現數據在PC上的實時顯示。本設計的成本還不到市場上同性能產品的1/2,更適用于教學等對產品數量要求較多,性能要求中等的單位采用

下一篇: PLC、DCS、FCS三大控

上一篇: 索爾維全系列Solef?PV

型號:LZMN2-A200

價格:面議

庫存:10

訂貨號:LZMN2-A200

型號:ESR5-NO-41-24VAC-DC

價格:面議

庫存:10

訂貨號:ESR5-NO-41-24VAC-DC

型號:DILA-22C(220-230V50HZ)

價格:面議

庫存:10

訂貨號:DILA-22C(220-230V50HZ)

型號:FAZ-C25/3

價格:面議

庫存:10

訂貨號:FAZ-C25/3

型號:PKZM0-1,6-SC

價格:面議

庫存:10

訂貨號:PKZM0-1,6-SC

型號:1-4-28X15

價格:面議

庫存:10

訂貨號:1-4-28X15